## PINE TECHNOLOGY PT-524G, PT-528G (VER.2)

Card Type Video Chip Set Highest Resolution Supported Maximum Video Memory Data Bus Video Types Supported Video card Cirrus Logic 1280 x 1024 2MB RAM (with GD-5428 chip) 32-bit VESA Local Bus XVGA

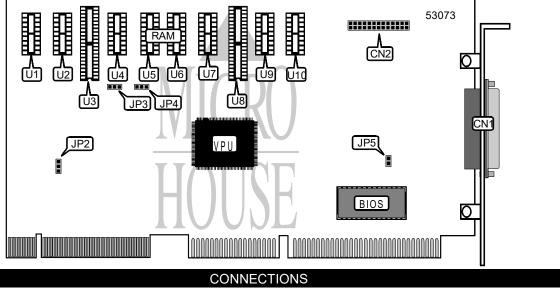

| Function                 | Label | Function          | Label |

|--------------------------|-------|-------------------|-------|

| 15-pin analog video port | CN1   | Feature connector | CN2   |

| USER CONFIGURABLE SETTINGS                     |       |                   |  |  |

|------------------------------------------------|-------|-------------------|--|--|

| Function                                       | Label | Position          |  |  |

| Wait State for LBA enabled                     | JP2   | Pins 2 & 3 closed |  |  |

| Wait State for LBA disabled                    | JP2   | Pins 1 & 2 closed |  |  |

| IRQ 9 enabled                                  | JP5   | Closed            |  |  |

| IRQ 9 disabled                                 | JP5   | Open              |  |  |

| Note: Exact location of pin 1 is unidentified. |       |                   |  |  |

| MEMORY BANKS SELECTION                                                                                   |                          |                   |                   |  |

|----------------------------------------------------------------------------------------------------------|--------------------------|-------------------|-------------------|--|

| Bank 0                                                                                                   | Bank 1                   | JP3               | JP4               |  |

| U3 & U8                                                                                                  | U1, U2, U4 - U7, U9, U10 | Pins 1 & 2 closed | Pins 1 & 2 closed |  |

| U1, U2, U4 - U7, U9, U10                                                                                 | U3 & U8                  | Pins 2 & 3 closed | Pins 2 & 3 closed |  |

| Note: Bank 0 and bank 1 are determined by JP3 and JP4 settings. Exact location of pin 1 is unidentified. |                          |                   |                   |  |

| RAM CONFIGURATION                                                                      |               |                |  |  |

|----------------------------------------------------------------------------------------|---------------|----------------|--|--|

| Size                                                                                   | Bank 0/1      | Bank 1/0       |  |  |

| 1MB                                                                                    | (8) 256KB X 4 | None           |  |  |

| 1MB                                                                                    | None          | (2) 256KB X 16 |  |  |

| 2MB (with GD-5428 chip)                                                                | (8) 256KB X 4 | (2) 256KB X 16 |  |  |

| 2MB (with GD-5428 chip)                                                                | (8) 256KB X 4 | (2) 256KB X 16 |  |  |

| Note: Bank 0 and Bank 1 are determined by JP3 & JP4 jumper settings. (See above table) |               |                |  |  |