Card Type Multi I/O

Chipset Controller Unidentified

I/O Options Game/MIDI port, memory, parallel port, serial port

Maximum DRAM 384KB

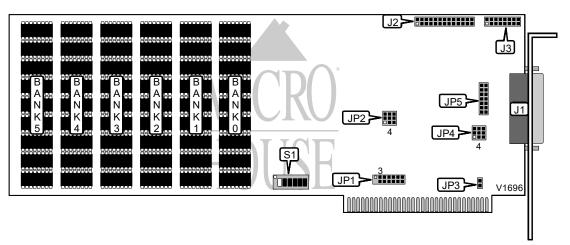

| CONNECTIONS                    |          |                          |          |

|--------------------------------|----------|--------------------------|----------|

| Purpos :                       | Location | Purpos :                 | Location |

| 25-pin serial port interface   | J1       | Game/MIDI port interface | J3       |

| 26-pin parallel port interface | J2       |                          |          |

| STARTING MEMORY ADDRESS |         |      |      |      |

|-------------------------|---------|------|------|------|

| Memory                  | Address | S1/1 | S1/2 | S1/3 |

| NONE                    | 00000h  | Off  | Off  | Off  |

| 64KB                    | 10000h  | Off  | Off  | On   |

| 128KB                   | 20000h  | Off  | On   | Off  |

| 192KB                   | 30000h  | Off  | On   | On   |

| 256KB                   | 40000h  | On   | Off  | Off  |

| 320KB                   | 50000h  | On   | Off  | On   |

| 384KB                   | 60000h  | On   | On   | Off  |

| 448KB                   | 70000h  | On   | On   | On   |

Continued next page. . .

. . . continued from previous page.

| MEMORY INSTALLED |      |      |      |

|------------------|------|------|------|

| Bank             | S1/4 | S1/5 | S1/6 |

| NONE             | Off  | Off  | Off  |

| 0                | Off  | Off  | On   |

| 1                | Off  | On   | Off  |

| 2                | Off  | On   | On   |

| 3                | On   | Off  | Off  |

| 4                | On   | Off  | On   |

| 5                | On   | On   | Off  |

| PARITY   | CHECK  |

|----------|--------|

| Setting  | JP3    |

| Enabled  | Closed |

| Disabled | Open   |

| CLOCK SELECT |                   |  |

|--------------|-------------------|--|

| Setting      | JP2               |  |

| í Clock 2    | Pins 8 & 9 closed |  |

| Clock 1      | Pins 7 & 8 closed |  |

| SERIAL PORT INTERRUPT |                   |  |

|-----------------------|-------------------|--|

| IRQ JP1               |                   |  |

| 3                     | Pins 1 & 3 closed |  |

| 4                     | Pins 3 & 4 closed |  |

| CLOCK INTERRUPT |                     |  |

|-----------------|---------------------|--|

| IRQ             | JP1                 |  |

| 2               | Pins 11 & 12 closed |  |

| 4               | Pins 5 & 6 closed   |  |

| 5               | Pins 7 & 8 closed   |  |

| 7               | Pins 9 & 10 closed  |  |

| PARALLEL PORT INTERRUPT |                     |  |

|-------------------------|---------------------|--|

| IRQ                     | JP1                 |  |

| 7                       | Pins 13 & 14 closed |  |

Continued next page. . .

. . . continued from previous page.

| PARALL      | EL PORT           |

|-------------|-------------------|

| Setting     | JP2               |

| LPT1 (378h) | Pins 4 & 5 closed |

| LPT2 (278h) | Pins 5 & 6 closed |

| SERIAL PORT |                   |  |

|-------------|-------------------|--|

| Setting JP2 |                   |  |

| COM1 (3F8h) | Pins 1 & 2 closed |  |

| COM2 (2F8h) | Pins 2 & 3 closed |  |

| CTS SIGNAL  |                   |  |

|-------------|-------------------|--|

| Setting     | JP4               |  |

| Normal      | Pins 1 & 4 closed |  |

| Forced high | Pins 4 & 7 closed |  |

| DSR SIGNAL  |                   |

|-------------|-------------------|

| Setting     | JP4               |

| Normal      | Pins 2 & 5 closed |

| Forced high | Pins 5 & 8 closed |

| DCD SIGNAL               |                   |  |  |  |

|--------------------------|-------------------|--|--|--|

| Setting                  | JP4               |  |  |  |

| Normal Pins 3 & 6 closed |                   |  |  |  |

| Forced high              | Pins 6 & 9 closed |  |  |  |

| SERIAL PORT INTERFACE CONFIGURATION |         |  |  |  |  |  |

|-------------------------------------|---------|--|--|--|--|--|

| JP5                                 |         |  |  |  |  |  |

| DTE                                 | DCE     |  |  |  |  |  |

|                                     |         |  |  |  |  |  |

|                                     |         |  |  |  |  |  |

| ■■                                  | <b></b> |  |  |  |  |  |

| <b></b>                             | <b></b> |  |  |  |  |  |

| <u> </u>                            | <b></b> |  |  |  |  |  |

| <u></u>                             |         |  |  |  |  |  |

|                                     |         |  |  |  |  |  |

Continued next page. . .

. . . continued from previous page.

| DRAM CONFIGURATION |             |             |             |             |             |             |  |

|--------------------|-------------|-------------|-------------|-------------|-------------|-------------|--|

| Size               | Bank 0      | Bank 1      | Bank 2      | Bank 3      | Bank 4      | Bank 5      |  |

| 64KB               | (9) 64K x 1 | NONE        | NONE        | NONE        | NONE        | NONE        |  |

| 128KB              | (9) 64K x 1 | (9) 64K x 1 | NONE        | NONE        | NONE        | NONE        |  |

| 192KB              | (9) 64K x 1 | (9) 64K x 1 | (9) 64K x 1 | NONE        | NONE        | NONE        |  |

| 256KB              | (9) 64K x 1 | NONE        | NONE        |  |

| 320KB              | (9) 64K x 1 | NONE        |  |

| 384KB              | (9) 64K x 1 |  |