## QUATECH, INC.

DS-2000/3000

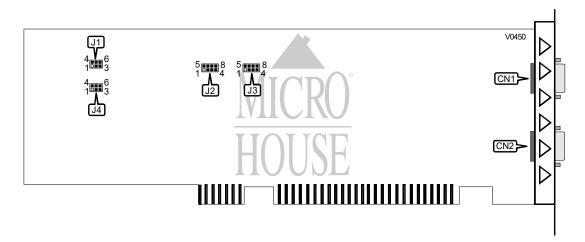

Card Type Chipset/Controller I/O Options Maximum DRAM

Serial controller 16550 Serial ports (2) N/A

| CONNECTIONS   |          |               |          |  |

|---------------|----------|---------------|----------|--|

| Purpo: :      | Location | Purpose       | Location |  |

| Serial port 1 | CN1      | Serial port 2 | CN2      |  |

| DTR CONFIGURATION |                          |  |

|-------------------|--------------------------|--|

| Setting           | J4                       |  |

| í - DTR           | Pins 2 & 3, 5 & 6 closed |  |

| + DTR             | Pins 1 & 2, 4 & 5 closed |  |

| INPUT CLOCK CONFIGURATION |                                 |  |  |  |

|---------------------------|---------------------------------|--|--|--|

| MHz                       | J1                              |  |  |  |

| í 1.8432MHz               | Pins 1 & 4, 2 & 3, 5 & 6 closed |  |  |  |

| 3.6864MHz                 | Pins 2 & 3, 4 & 5 closed        |  |  |  |

| 9.216MHz                  | Pins 1 & 2, 5 & 6 closed        |  |  |  |

| 18.432MHz                 | Pins 2 & 5 closed               |  |  |  |

Continued on next page . . .

## QUATECH, INC.

DS-2000/3000

. . . continued from previous page

| TRANSMIT/RECEIVE CONFIGURATION |                                           |  |

|--------------------------------|-------------------------------------------|--|

| Function                       | J2                                        |  |

| RTS/CTS loopback               | Pins 1 & 5 closed, pins 1 & 2 open        |  |

| Transmit RTS                   | Pins 5 & 6 closed, pins 6 & 7 open        |  |

| Receive RTS                    | Pins 1 & 2 closed, pins 2 & 3 open        |  |

| RCLK/XCLK loopback             | Pins 3 & 7 closed, pins 2 & 3 open        |  |

| Transmit XCLK                  | Pins 6 & 7 closed, pins 5 & 6 open        |  |

| Receive RCLK                   | Pins 2 & 3 closed, pins 1 & 2 open        |  |

| AUX OUT/AUX IN loopback        | Pins 2 & 6 closed, pins 5 & 6, 6 & 7 open |  |

| Half Duplex                    | Pins 4 & 8 closed                         |  |

| Full Duplex                    | Pins 4 & 8 open                           |  |