SiS 55x (SiS 55x Core)

Release date

File

Logs

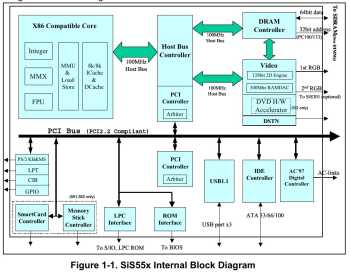

Integrated x86 Rise MP6 Kirin CPU

- X86 Instruction Set Compatible Processor

- Superscalar Execution

- Three Superpipelined Integer Units

- Pipelined Floating Point Unit

- Innovative Instruction Decode and Branch Prediction

- Separate Code and Data Caches

- Support for Bus Frequency up to 100MHz

- Low Power Consumption Design

- Software Compatibility with Microsoft Windows, Windows CE, MS-DOS, QNX and LINUX

- Supports Host Bus Direct Access GUI Engine for Integrated A.G.P. VGA Controller

Integrated DRAM Controller

- Supports up to 2 Double Sided DIMMs (4 Rows Memory)

- Supports PC100/PC133 SDRAM Technology

- Supports NEC Virtual Channel Memory (VC-SDRAM) Technology

- System Memory Size up to 1 GB

- Supports 16Mb, 64Mb, 128Mb, 256Mb, 512Mb SDRAM Technology

- Supports Suspend-To-RAM (STR)

- Relocatable System Management Memory Region

- Programmable Buffer Strength for CS#, DQM[7:0], WE#, RAS#, CAS#, CKE, MA[14:0] and MD[63:0]

- Shadow RAM Size from 640KB to 1MB In 16KB Increments

- Two Programmable PCI Hole Areas

Integrated A.G.P. Compliant Target Host-To-PCl Bridge

- AGP V2.0 Compliant

- Supports Graphic Window Size from 4Mbytes To 256Mbytes

- Supports Pipelined Process in CPU-To-Integrated A.G.P. VGA Access

- Supports 8 Way, 16 Entries Page Table Cache for GART to Enhance Integrated VGA Controller Read/Write Performance

- Supports PCI-To-PCl Bridge Function for Memory Write from 33Mhz PCI Bus to Integrated A.G.P. VGA

High Performance PCI Arbiter

- Supports up to 3 external PC| Masters

- Rotating Priority Arbitration Scheme

- Advanced Arbitration Scheme Minimizing Arbitration Overhead

- Guaranteed Minimum Access Time for CPU And PCI Masters

Integrated Host-To-PCI Bridge

- Zero Wait State Burst Cycles

- CPU-To-PClI Pipeline Access

- 256B to 4KB PCI Burst Length for PCI Masters

- PCI Master Initiated Graphical Texture Write Cycles Re-Mapping

- Reassembles PCI Burst Data Size into Optimized Block Size

Fast PCI IDE Master/Slave Controller

- Supports PCI Bus Mastering

- Supports Native Mode and Compatibility Mode

- Supports PIO Mode 0, 1, 2, 3, 4

- Supports Multiword DMA Mode 0, 1, 2

- Supports Ultra DMA 33/66/100

Advanced PCI H/W Audio & S/W Modem

- Hardware DirectSound™ accelerator

- 64-Channel DirectSound™ acceleration with High Quality sampling rate converter.

- 64-Voice DirectSound™ 3D Channels.

- 16 On-Chip High-Precision re-routable Sub-Mixers.

- Full-duplex supports of Stereo/Mono, 8-/16-bits, and Signed/Unsigned Samples.

- Per Channel Control of Volume and Pan.

- Advanced DLS-2 compliant Wavetable Synthesizer

- 64-Voices Polyphony Wavetable Synthesizer fully compliant with DLS-2.

- Per Channel control of Volume, Envelope, Pitch, Pan, Tremolo, and Vibrato etc.

- Per Channel Resonance and Cut-Off Frequency control of Low-Pass Filter.

- Fully Compliant with AC97 V2.1

- Support for up to 3 AC97 CODEC's.

- Support for AC3 2-/4-6-channels Output over AC-link.

- Support for DRC and VRC over AC-link.

- Support ever slot defined in AC97 V2.1.

- Power Management Control of AC97 CODEC.

- Telephony & Modem

- Full-Duplex Support for Line1 and Line2 over AC-link.

- Full-Duplex Support for Handset over AC-link.

- (**) Consumer Digital Audio Interface

- Support PCM/AC-3 output.

- Support AC97 CODEC's output.

Advanced Power Management

- Meets ACPI 1.0 Requirements

- Meets APM 1.2 Requirements

- ACPI Sleep States Include S1, S2, S3, S4, S5

- CPU Power States Include CO, C1, C2, C3

- Power Button with Override

- RTC Day-Of-Month, Month-Of-Year Alarm

- 24-Bit Power Management Timer

Last updated 2019-04-30T00:00:00Z

Disclaimer

The info found in this page might not be entirely correct. Check out this guide to learn how you can improve it.

Image 1 of 2 (Rigo "0xCats" Reddig)

Image 1 of 2 (Rigo "0xCats" Reddig)

Image 2 of 2 (Rigo "0xCats" Reddig)

Image 2 of 2 (Rigo "0xCats" Reddig)